光メディアインタフェース研究室 助教の田中です.前回の投稿は,2015年3月「光メディアインタフェース研究室 本格始動!」でした.あの時は,研究室が発足したばっかりでしたが,いまや学生はM1からD3まで勢揃いの立派な研究室になりました.今回は,これまでの本研究室の成果を振り返ってみます.

光メディアインタフェース研究室は,1.機械がカメラを通して現実を理解する「コンピュータビジョン」 2.あらゆる物体の質感をリアルに再現する「コンピュータグラフィクス」 3.カメラの常識を打ち破る新しい撮影技術「コンピューテーショナルフォトグラフィ」 4.あらゆる研究の基礎となる「光学設計」の4本柱で研究を進めており,人間と機械が光を媒体としてシーンに関する情報を共有できる新しいインタフェースの実現を目指し活動しています.詳しい研究内容は,研究室ホームページ をご参照ください.

今,光メディアインタフェース研究室には,教授・准教授・2名の助教の計4名の教員,事務補佐員,6名の博士後期課程学生,16名の博士前期課程学生,さらに1名のインターン生で活動しています.研究室の学生は,毎年何らかの研究予算を自分で獲得してきてプロジェクトを進めるなど,活発な人が多く在籍しています.CICPと呼ばれる学内予算はもとより,日本学術振興会特別研究員や,JST ACT-I,IPA未踏スーパークリエーター認定などを得ており,自ら未開拓分野を切り拓いていく姿勢には感心します.これまでに,本研究室を修了した学生は,3年間で延べ21人となり,各方面で活躍しています.「光メディアインタフェース研究室出身はすごい」と呼ばれるよう,より一層の活躍を期待したいところです.また,これまで多数の留学生・インターン等を受け入れています.なぜだか分かりませんが,多くがフランス語圏からの留学生です.もしかして,フランス語の案内ページも作ったほうが良いのでしょうか…?

本研究室は,活発に外部の機関と共同研究を実施してきました.複数の国内大手電機メーカーや農業・医療・自動車産業,アニメ産業の企業と連携中あるいは連携してきました.アカデミックでは,東京大学・京都大学・大阪大学・九州大学・国立情報学研究所・筑波大学・広島大学・早稲田大学・東邦大学や,Carnegie Mellon University (CMU・アメリカ)・Arizona State University(アメリカ)・The University of Picardie Joule Verne (フランス)・The University of California Los Angeles (UCLA・アメリカ) の研究者と共同研究を実施してきました.プロジェクトの数が多く,学生が多数の幅広いテーマから自分のやりたいことを選択し取り組めるのも,この研究室の大きな特徴かもしれません.

彼らとともに成し遂げた研究プロジェクトは http://omilab.naist.jp/publications-jp.html から見ることができます.数字で見ていくと,情報電子通信学会論文賞やMIRU長尾賞などの大きな賞を含む24個の受賞,2本のPAMI(最難関国際論文誌)を含む12本の論文誌および5本のCVPR(最難関国際会議)を含む21本の査読付き国際会議論文を発表してきました.どのテーマで研究しても,在学中に1回以上の発表を学会で行うべく,ハイレベルな研究活動を行っています.

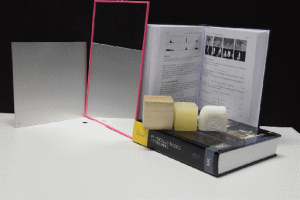

ここで,大きな賞を受賞した2つの研究を少し紹介したいと思います.一つ目は,電子情報通信学会論文賞やMIRUフロンティア賞を受賞している,一連の新しいコンピュータグラフィクス(CG)の研究です.多くの人は,CGと聞くと,ゲームや映画で使われているようなきれいな画を作る技術だと思われているでしょう.これまでのCG技術の一つに,現実の物体を計測し,それそっくりな見た目の映像を計測データを使って「画面上で」リアルに表現するというものがありました.我々の研究室では,この「画面上」という制限を取っ払って,「リアル空間で」計測した物体そっくりのレプリカをつくろうという新しい表現方法を研究しています.つまり,物体の形状と質感を,3Dプリンタや高度な印刷技術,微細構造の工夫などによって,現実空間にコピーする技術の開発を行っています.図1にこの研究の例を示しています.この実験では,計測したサーモンの質感を,ロウでできた物体にコピーしています.写真ではわかりにくいかもしれませんが,どこからみてもサーモンっぽい質感の再現に成功しました.この技術が発展すれば,本物の美術品や古典籍にそっくりな触れるレプリカの作成,個人個人の肌とそっくりな義手・義足や,エンターテインメントなど,コンピュータグラフィクス技術の新しい社会実装に貢献できるのではないかと考えています.

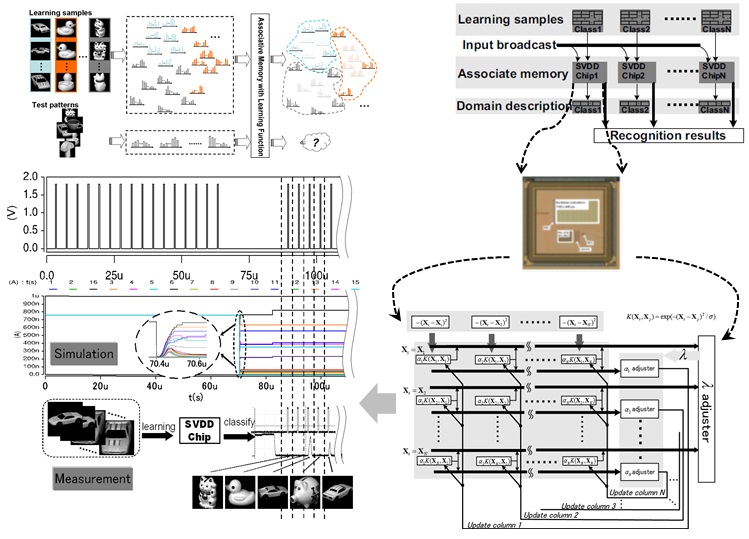

2つ目の研究は,MIRU長尾賞という,いわゆる日本一と認められた,新しいコンピュータビジョンの研究です.コンピュータビジョンというと,カメラで撮影された視覚情報をコンピュータでどのように理解するか,という風に説明されてきました.我々の研究室では,カメラで撮影された後の2次元画像からスタートしているようでは情報が不十分であり,画像になる前の,現実世界を飛び交う光の状態からシーン理解を行うべきだという信念のもと,より次元を増やした計測からシーン理解を行う研究を行っています.その中でも,時間の次元を増やす,ということに関して,世界のトップレベルとしのぎを削っています.時間の次元と言っても,単にビデオやハイスピードカメラで撮影するということではありません.この研究室で行っているのは,「光」自体が伝わっていく様子を可視化できるくらいの超高速な計測,時間で言うと数ナノ秒(0.000000001秒)から数ピコ秒(0.000000000001秒)です.図2に,実際に 250ピコ秒で撮影した画像を載せています.このレベルになると,光がどのように反射・散乱し,シーン中を伝わっていくのかが分かります.当然ながら,こうした情報を使うと,3次元形状,物体の材質,異常検知などが簡単に行えるようになります.

光メディアインタフェース研究室では,現在,向川教授を研究代表とした大型プロジェクト「多元光情報の符号化計測と高次元化処理の協調設計」を実施しています.このプロジェクトでは,計測の次元を「時間」だけでなく,「波長」や「空間」といった次元にも拡張していき,高度な計測技術を確立することを目指しています.博士課程やポスドクとして参画したい方,コンタクトください.

最後に,NAISTへの入学を検討している方や,インターン希望の方,ぜひ一度光メディアインタフェース研究室に見学に来てください.文章ではわからない研究のこと,研究室の雰囲気,研究の進め方,などなど,今後の進路に役立つこと間違いありません.NAISTでは,受験生のためのオープンキャンパス を毎年2月と5月に行っています.また,受験を検討している人のために2・3日の研究体験ができるサマーセミナー (8月頃)や スプリングセミナー (2月頃)もやっています.さらに,いつでも見学会 という制度を使うと,研究室が受け入れ可能な日はいつでも見学・相談が可能です.ぜひ,ご検討ください.